- Home

-

Optiger Lens

-

Bi-telecentric Lens

- German Designed Optiger TTL06 Series

- German Designed Optiger TTL08 Series

- German Designed Optiger TTL9.5 Series

- German Designed Optiger TTL11.5 Series

- German Designed Optiger TTL16 Series

- German Designed Optiger TTL18.5 Series

- German Designed Optiger TTL23 Series

- German Designed Optiger TTL28.5 Series

- German Designed Optiger TTL39.2 Series

- German Designed Optiger TTL44 Series

- Telecentric Lens

-

Bi-telecentric Lens

- Canary lens

- Optiger Light Source

- Related Products

- Technical Support

- About Us

-

Company Gallery

- Contacts

Related Products

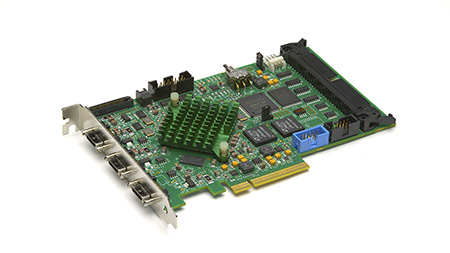

Product Description

With each successive generation of Camera Link frame

grabbers, BitFlow has improved the quality, flexibility, and robustness of

their interfaces. Meanwhile, the Camera Link Specification has also been

continuously evolving: 80-bit (10-tap) mode was added, Power over Camera Link

(PoCL), new connectors, new tap formats. The Axion-CL uses the Cyton-CXP's

backend: the StreamSync DMA engine and buffer manager, as well as a brand new

PCIe Gen 2 interface, with DMA optimized for modern computers.

The Virtual Frame Grabber

The Axion supports up to two cameras. In dual camera mode, the board looks to Windows and application software like two completely independent frame grabbers. This simplifies the setup for multiple cameras as each camera is really treated separately. Of course, the cameras can be internally synchronized if needed, but they can also be run completely independently. The two cameras do not have to be the same resolution, frame rate, trigger mode, or even tap format.

StreamSync

The StreamSync system consists of an Acquisition Engine and a Buffer Manager. The StreamSync system is a start-from-scratch complete redesign of the acquisition and DMA parts of a frame grabber.

StreamSync Features

>> Efficient support for variable

sized images with fast context switches between frames

>> Per frame control of acquisition

properties (AOI specifically)

>> Hardware control of image

sequencing

>> Enhanced debug capabilities

>> Efficient support for on-demand

buffer allocation (Genicam model)

>> Graceful recovery from dropped packets (either on the input side or the DMA side)

PCI Express Gen 2.0 Interface

The Axion-CL has a Gen 2.0 x4 PCI Express bus interface. The Gen 2.0 PCIe bus doubles the data rate of the Gen 1.0 bus while using the same footprint and connectors. The Axion-CL is fully backwards compatible with Gen 1.0 motherboards, though the data rate will be halved.

Camera Control and I/O

Supported by a GUI camera file editing

utility (CamEd), the Axion-CL can acquire fixed or variable size images and

features a programmable ROI (Region Of Interest) sub-windowing capability. The

board provides a full set of camera control signals (CC1, CC2, CC3, CC4) and

sync inputs (LVAL, FVAL, PCLK, trigger, and encoder) for each camera connected

to the board (up to two cameras can be connected). These signals are completely

independent, although there are provisions for driving all cameras from a

signal set up encoder/trigger signals. There is also a large number of

programmable general purpose outputs and inputs that are not tied to the

camera's timing.

I/O signals can be routed to/from many

internal and external destinations, providing a flexible routing that is

unprecedented in the industry. In addition, there are separate hardware I/O

signals which can be connected to/from an external source. Finally, each CL

camera has a full set of these signals which can be run independently. The

Axion-CL board, as with our past interface products, supports not only simple

triggering modes but also complicated, application-specific triggering and

control interactions with your hardware environment.

Specifications

>> Camera Link 2.0 Compliant

>> Supports up to two cameras

>> Supports base, medium, full,

80-bit (10-tap) CL cameras

>> Supports CL clocks up to 85 MHz

>> Supports simultaneous capture from

two 80-bit/85 MHz cameras

>> Industry standard SDR Camera Link

connectors

>> Support PoCL and non-PoCL cameras

>> Support dual connector PoCL

>> Provides Safe Power, full

protection from all power line faults

>> Cameras can be accurately

synchronized, or can be completely independent

>> PCI Express x4 Gen 2.0 interface

(also works in x8 and x16 slots)

>> Compatible with PCI Express Gen

1.0 slots

>>Separate I/O for each camera

>> Highly deterministic, low latency

frame grabber to camera trigger

>>Supports simultaneous

communications to all cameras

>> Windows "sees" a

separate frame grabber for each camera

>> No on-board memory is needed

>> StreamSync acquisition engine

optimizes synchronization between acquisition and DMA

>>StreamSync buffer manager maximize

DMA channel efficiency

>> Acquire variable length frames

from line scan cameras

>> Acquire image sequences well

beyond the 4GB barrier

>> No frame rate limit

>> Triggers and encoders for external

control of acquisition

>>Programmable signal generator for

camera control (independent for each camera)

>>Quadrature encoder support

including sophisticated triggering schemes

>>Encoder divider/multiplier

>>Drivers, utilities, and examples

for Windows and Linux

>>Supported on both 32-bit and

64-bit platforms

>>Drivers for most 3rd party

processing environments (e.g. HALCON, LabView, VisionPro, MATLAB, etc.)

>>Full GenICam support for control and

capture

>>RoHS compliant

站用透明_m9M5aQ.png)

號二維碼網(wǎng)站底部.jpg)

站[2].png)

站用透明.png)

號二維碼網(wǎng)站右側(cè).jpg)